Интерфейсы и интерфейсные БИС.

Подключение внешних устройств к системной шине часто осуществляется посредством электронных схем, называемых контроллерами ВВ (интерфейсными БИС). Разнообразные ПУ сопрягаются с МП – системой посредством небольшого числа унифицированных интерфейсных БИС. В их функции кроме непосредственно ВВ водит формирование периферийного интерфейса, то есть преобразование машинных данных в формат, необходимый устройству, и наоборот; перенос протокола обмена с МП на более высокий уровень, электрическое согласование сигналов.

Гибкость и универсальность интерфейсных БИС достигается путем программирования выполняемых ими функций. Для каждого МП выпускается набор вспомогательных БИС, образующий микропроцессорный комплект (МПК). Набор вспомогательных БИС для процессоров 8080\8085 фирмы INTEL, удовлетворяющих требованиям на шину MICROBUS, включает в себя около 20 микросхем. Рассмотрим наиболее популярные интерфейсные БИС этого семейства и их применение.

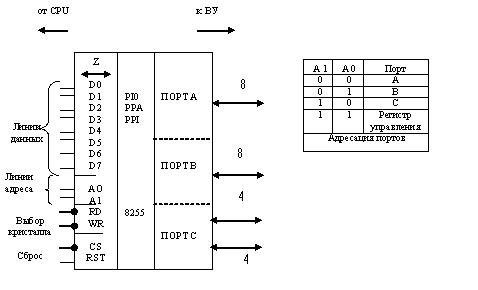

Микросхема программируемого параллельного ввода-вывода (PIO) предназначена для передачи данных через 8 – битные порты в ВУ. УГО типичной микросхемы PIO и распределение адресов между регистрами в PIO показаны на рис.5.7. Байт данных передается по шине данных, а две линии адреса А0 и А1 обеспечивают адреса 4-х регистров PIO. Регистр управления при записи применяется для выбора направлений портов и режимов передачи. При чтении в определенном режиме регистра управления можно получить информацию и состоянии процесса обмена с ВУ.

Рис 5.7. Микросхема программируемого параллельного ввода-вывода.

Типовыми режимами параллельного ввода-вывода являются: прямой однонаправленный ввод или вывод, ввод или вывод с квитированием и двунаправленный ввод-вывод. Выбор режима задается форматом управляющего слова в регистре управления.

Наиболее широко распространенными PIOдля 8085 являются м./сх 8255 и 8155 фирмы Intel. Формат управляющего слова и режимы для PIO 8255 приведен на рис. 5.8.

Рис 5.8. Формат управляющего слова для PIO8255.

Рис 5.9. Ввод с квитированием для PIO8255.

Одним из типовых вариантов является подключение через микросхему программируемого параллельного ввода-вывода микросхем АЦП и ЦАП к магистрали МПС..

Рис 5.10. Подключение микросхем АЦП и ЦАП через PIOк магистрали МПС.

Рис 5.11. Формат управляющего слова и программирование PIOдля работы с АЦП.

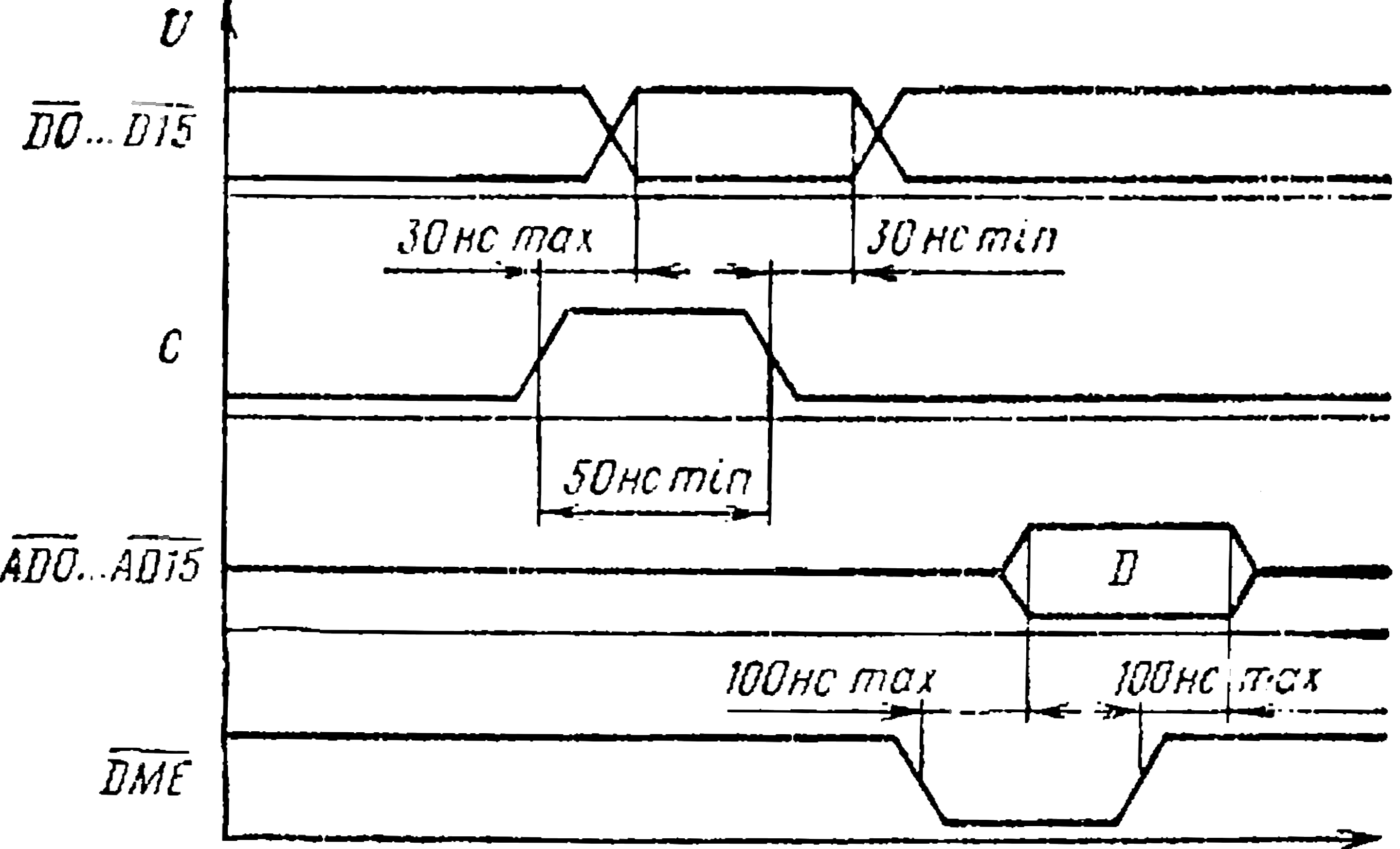

Рис 5.12. Временные диаграммы работы PIOи АЦП.

Функции контактов 8155 приведены на рис.5.9, 5.10, инициализация и пример применения 8255 приведены на рис.5.11—5.12.

Универсальный асинхронный приемопередатчик(UART) применяется для организации последовательного ввода-вывода, т. е. когда требуется передать 8 бит по одной 2 –проводной линии. При асинхронной передаче 8 –и битный символ данных окаймляется стартовым и стоповым битами. Регистр управления перед началом передачи должен быть инициализирован и выбраны параметры: скорость передачи, число стартовых и стоповых бит, паритет. Поскольку микросхемы UART работают с TTL уровнями, а последовательный интерфейс, например RS-232c, требует других сигналов, то для соединения UART с разъемом последовательного интерфейса требуется схема преобразователя уровней.

Стандартным UART, через который система с 8085 подключается к линии связи является 8251. Микросхема содержит 4 адресуемых регистра, которые выбираются сигналами A0,RD,WR в соответствии с табл.3. Внешние соединения 8251 приведены на рис 5.13, а формат управляющего слова на рис.5.14. регистр управления также используется для задания коэффициента деления частоты (1,16, 64). Для получения всего диапазона скоростей частота должна быть переменной и программируемой(например, счетчик в 8155).

В качестве примера контроллера на 8085 и содержащего RAM, ROM, PIOиUART на рис 5.15. показана схема кассового аппарата.

Не забудь поделиться страницей с друзьями:

Главная | Случайная страница | Трендовая

КАЗАНСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

им. А.Н. ТУПОЛЕВА

А. Н. БОРИСОВ

Борисов А.Н. Программируемые БИС микропроцессорных систем: Учебное пособие. Казань: Изд-во Казан. Гос. техн. ун-та, 2003.

Рассматриваются особенности построения и функционирования программируемых БИС, применяемых в микропроцессорных системах на базе микропроцессора К1810. Приведены структурные схемы БИС, режимы работы, излагается методика программирования БИС и особенности применения БИС в МПС.

Предназначено для студентов высших учебных заведений заочного, очного обучения и экстерната по специальностям “Вычислительные машины, комплексы, системы и сети”, “Автоматизированные системы обработки информации и управления”, “Информационные системы и технологии”.

Табл. 5. Ил. 31. Библиогр.: 4 назв.

Рецензенты:кафедра радиофизики Казанского государственного

доцент, канд. техн. наук В. Ю. Порфирьев.

В в е д е н и е

Программируемые большие интегральные схемы (БИС) – это БИС, выполняющие сложные функции, используемые в аппаратуре микропроцессорных систем (МПС).

Почему они называются программируемыми? Каждая из программируемых БИС может работать в одном из нескольких предназначенных для этой БИС режимах. Для каждого режима могут быть заданы различные рабочие параметры. В зависимости от типа БИС количество задаваемых режимов и рабочих параметров может быть самым разнообразным. Перед началом работы МПС, входящие в ее схему БИСы программируют (инициализируют), т.е. задают начальный режим работы БИС и конкретные рабочие параметры для заданного режима. В случае необходимости пользователь в процессе работы МПС может перепрограммировать любую программируемую БИС, входящую в состав МПС

Существенное значение имеет возможность использования в МПС, построенных на базе микропроцессора К1810, совместимых с микропроцессорным комплектом серии К1810 программируемых БИС серии К580.

На практике при разработке и отладке МПС перед пользователем встает задача подсоединения БИС в аппаратуре МПС и создания соответствующего программного обеспечения для правильной работы БИС. Для этого необходимо знать архитектуру БИС, представлять взаимодействие БИС в системе и овладеть программированием БИС прежде всего на языке ассемблера.

Типы программируемых БИС.

1. Интерфейсные БИС. К ним относятся БИС, позволяющие организовать различные режимы обмена между внешними устройствами, подключаемыми к МПС, и центральным процессором (ЦП) МПС. Из этой группы программируемых БИС отметим:

· параллельный программируемый интерфейс КР580ВВ55А, предназначенный для обмена информацией в параллельном коде;

· последовательный программируемый интерфейс КР580ВВ51А, предназначенный для обмена информацией в последовательном коде.

2. Большие интегральные схемы, предназначенные для выполнения сложных функций в МПС. Например, для выполнения обработки прерываний при запросах от внешних устройств используется БИС К1810ВН59 – программируемый контроллер прерываний; для организации режима прямого доступа к памяти (ПДП) – БИС К1810ВТ37 – программируемый контроллер ПДП; для счета временных интервалов – БИС К1810ВИ54 – программируемый таймер.

Общая структура программируемых БИС.

Организация передачи данных, управляющей информации для программируемых БИС, сигналов квитирования и синхронизации осуществляется ЦП. Обращение ЦП к программируемым БИС осуществляется через программно-доступные элементы БИС (обычно это одно- или двухбайтовые регистры), логические адреса которых называются портами ввода-вывода. Обращение к ним организуется с помощью команд

ввода-вывода IN, OUT по соответствующим адресам портов.

Регистры программируемых БИС функционально различны. Одни из них предназначены для буферизации передаваемых данных, другие – для хранения информации о состоянии самой БИС и состоянии ВУ (эту информацию может проанализировать ЦП). Третьи – для приема и обработки приказов от ЦП, управляющих действиями БИС. Четвертые – для восприятия рабочих параметров, конкретизирующих заданные приказы.

У рассматриваемых в данном пособии программируемых БИС есть одинаковые по назначению выводы. К ним относятся:

· D7-D0 (данные). Эти выводы подключаются к шине данных системного интерфейса МПС. Через них происходит обмен информацией между ЦП и регистрами БИС.

·  (чтение). На этот вывод подается системный сигнал

(чтение). На этот вывод подается системный сигнал  на выдачу данных из БИС в ЦП. Сигнал формируется при выполнении команды IN.

на выдачу данных из БИС в ЦП. Сигнал формируется при выполнении команды IN.

·  (запись). На этот вывод подается системный сигнал

(запись). На этот вывод подается системный сигнал  , по которому данные поступают с шины данных системного интерфейса в адресуемый порт БИС. Сигнал формируется при выполнении команды OUT.

, по которому данные поступают с шины данных системного интерфейса в адресуемый порт БИС. Сигнал формируется при выполнении команды OUT.

·  (выбор БИС). Идентифицирует обращение к БИС путем дешифрации старших разрядов адреса. При активном сигнале (

(выбор БИС). Идентифицирует обращение к БИС путем дешифрации старших разрядов адреса. При активном сигнале (  =0) БИС активна и может обмениваться данными с ЦП.

=0) БИС активна и может обмениваться данными с ЦП.

При  =1 выводы D7-D0 находятся в третьем состоянии.

=1 выводы D7-D0 находятся в третьем состоянии.

Во всех рассматриваемых программируемых БИС входным блоком является восьмиразрядный буфер данных, обеспечивающий двунаправленную связь внутренней шины БИС с шиной данных системного интерфейса МПС.

Для подключения к шинам МПС внешних устройств (ВУ) используются интерфейсные БИС. Эти БИС позволяют организовать различные режимы обмена данными между центральным процессором и ВУ. Данные могут передаваться от ВУ (ввод) или к ВУ (вывод) в параллельном коде либо в последовательном. В первом случае применяется параллельный интерфейс связи, во втором – последовательный.

1.1. Параллельный периферийный интерфейс

В МПС, построенных на базе микропроцессора К1810, для организации обмена данными между ЦП и ВУ предназначен параллельный периферийный интерфейс (ППИ) БИС КР580ВВ55А. Это программируемое устройство, которое организует обмен 8-разрядными данными через 3 двунаправленных канала А, В и С. Направление обмена и режим работы каждого из каналов задаются программно. Каналы А и В не разделены, а линии канала С могут быть разделены на две четырехбитные группы, представляющие собой два независимых канала.

Структурная схема БИС КР580ВВ55А приведена на рис.1.1. В состав БИС ППИ входят:

· 8-разрядный двунаправленный трехстабильный буфер данных (БД), связывающий ППИ с системной шиной данных;

· блок управления записью-чтением, обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ;

· три 8-разрядных канала ввода-вывода А, В и С для обмена информацией с ВУ.

В канале А предусмотрены выходной регистр для приема данных с системной шины и выдачи их в ВУ и входной регистр для приема данных от ВУ и выдачи их на системную шину. В каналах В и С имеется по одному регистру, который обеспечивает передачу данных между ЦП и ВУ в требуемом направлении. Все каналы снабжены входными и выходными формирователями с тремя состояниями.

Рис. 1.1. Структурная схема БИС КР 580ВВ55А

В блоке управления находится регистр, называемый регистром управляющего слова (РУС). Настройка каждого из каналов ППИ на требуемый режим работы осуществляется засылкой управляющего слова из ЦП в РУС.

Управляющие сигналы выбора БИС (  ), чтения (

), чтения (  ) и записи (

) и записи (  ) подаются в блок управления ППИ. На выводы А1, А0 подключаются линии с адресной шины системного интерфейса. Информация на этих линиях определяет внутренний регистр ППИ, коммутируемый на шину данных:

) подаются в блок управления ППИ. На выводы А1, А0 подключаются линии с адресной шины системного интерфейса. Информация на этих линиях определяет внутренний регистр ППИ, коммутируемый на шину данных:

· 00 – канал А,

· 01 – канал В,

· 10 – канал С,

· 11 – регистр управляющего слова.

Управляющие сигналы вместе с адресными сигналами А1 и А0 определяют вид операции, выполняемой ППИ в соответствии с табл.1.1, где Х – безразличное состояние сигнала.

Отметим назначение выводов ППИ, которые еще не рассматривались:

– RESET – сброс БИС;

– РА7 – РА0 – выводы для соединения канала А с ВУ;

– РВ7 – РВ0 – выводы для соединения канала В с ВУ;

– РС7 – РС0 – выводы для соединения канала С с ВУ;

Каналы ППИ могут работать в разных режимах. Предусмотрено три режима работы: режим 0, режим 1, режим 2. Канал А может работать в любом из трех режимов, канал В – в режиме 0 или 1. Канал С может быть использован для передачи данных только в режиме 0. В других режимах его

регистр используется как своеобразный регистр состояния.

Перед началом использования БИС проводят его инициализацию. Для этого определяют режим работы и направление передачи данных для каждого канала. Эту информацию кодируют и в виде управляющего слова заносят в РУС ППИ.

Формат управляющего слов приведен на рис.1.2. Значение бита D7=1 указывает, что ЦП посылает информацию в 7-разрядный регистр РУС ППИ.

Режимы работы каналов можно изменять как в начале, так и в процессе выполнения программы. Это позволяет обслуживать различные ВУ в определенном порядке одной БИС. При изменении режима работы любого канала регистры всех каналов сбрасываются.

Канал А (РС3-РС0)

Канал А Канал В

Канал С (РС7-PС4) Канал В

Рис. 1.2. Формат управляющего слова

Режимы работы каналов ППИ.

· Режим 0 (простой ввод-вывод).

В этом режиме может работать любой из каналов ППИ. Каждый канал может работать либо на ввод, либо на вывод данных в зависимости от указанного в управляющем слове направления передачи данных.

Если производится ввод, то регистр канала по сигналу  коммутирует подключенное к каналу ВУ на шину данных системного интерфейса. Если выполняется вывод, то по сигналу

коммутирует подключенное к каналу ВУ на шину данных системного интерфейса. Если выполняется вывод, то по сигналу  информация с шины данных системного интерфейса появляется на выходах регистра канала. Канал С дополнительно может быть разделен на два четырехразрядных канала с выводами (РС7-РС4 и РС3-РС0). Сигналы квитирования в режиме 0 не формируются.

информация с шины данных системного интерфейса появляется на выходах регистра канала. Канал С дополнительно может быть разделен на два четырехразрядных канала с выводами (РС7-РС4 и РС3-РС0). Сигналы квитирования в режиме 0 не формируются.

По сигналу сброса RESET регистр управляющего слова ППИ устанавливается в состояние, при котором все каналы настраиваются на работу в режиме 0 для ввода данных.

· Режим 1 (стробируемый ввод-вывод)

В этом режиме могут работать каналы А и В. Выводы канала С используются для приема и выдачи сигналов управления (квитирования) обменом по каналам А и В, для выдачи сигналов запросов прерывания INTR в ЦП (для канала А – вывод РС3, для канала В – вывод РС0).

Рис. 1.3. Схема связи каналов ППИ с ВУ в режиме 1 (ввод):

а) канала А; б) канала В.

Структурные схемы связи ППИ с ВУ для работы каналов А и В в режиме 1 показаны на рис.1.3. (ввод) и на рис.1.4. (вывод).

Для операции ввода предназначены следующие управляющие сигналы:

–  (строб ввода) – входной сигнал от ВУ, который загружает данные, поступающие от ВУ, в регистр канала.

(строб ввода) – входной сигнал от ВУ, который загружает данные, поступающие от ВУ, в регистр канала.

– IBF (входной буфер загружен) – выходной сигнал подтверждения о загрузке данных в регистр канала.

– INTR (запрос прерывания) – сигнал, выдаваемый в ЦП на прерывание.

Операцию вывода характеризуют такие три сигнала:

–  (выходной буфер загружен) – выходной сигнал в ВУ о наличии данных на выходе канала.

(выходной буфер загружен) – выходной сигнал в ВУ о наличии данных на выходе канала.

–  (подтверждение) – входной сигнал от ВУ, подтверждающий получение данных из канала ППИ.

(подтверждение) – входной сигнал от ВУ, подтверждающий получение данных из канала ППИ.

– INTR (запрос прерывания) – сигнал, выдаваемый в ЦП на прерывание.

Рис. 1.4. Схема связи каналов ППИ с ВУ в режиме 1 (вывод):

а) канала А; б) канала В

Незадействованные для управляющих сигналов выводы канала С могут быть использованы для ввода-вывода данных. Направление передачи по этим выводам определяется в управляющем слове.

· Режим 2 (двунаправленная передача информации между ППИ и ВУ)

Режим 2 предназначен для двунаправленного обмена данными ЦП с ВУ только через канал А ППИ. При этом пять линий подключаемых к выводам канала С (РС7-РС3) выполняют функции управляющих сигналов (рис.1.5). В отличие от режимов 0 и 1 в режиме 2 направление передачи между каналом А и ВУ определяется не указаниями в управляющем слове, заносимым в РУС, а сигналами  (вывод) или

(вывод) или  (ввод), определяющими направление передачи между ЦП и ППИ.

(ввод), определяющими направление передачи между ЦП и ППИ.

Рис. 1.5. Схема связи канала А ППИ в режиме 2 с ВУ

При работе каналов в режимах 1 и 2 при вводе данных по стробирующему сигналу приема (  ), равному 0, данные записываются во входной регистр соответствующего канала. Выходной сигнал подтверждения приема ( IBF), равный 1, свидетельствует о том, что данные записаны в регистр канала. Сигнал запроса прерывания INTR=1 информирует ЦП о завершении приема информации в канале. Сигнал INTR сбрасывается спадом сигнала

), равному 0, данные записываются во входной регистр соответствующего канала. Выходной сигнал подтверждения приема ( IBF), равный 1, свидетельствует о том, что данные записаны в регистр канала. Сигнал запроса прерывания INTR=1 информирует ЦП о завершении приема информации в канале. Сигнал INTR сбрасывается спадом сигнала  .

.

При выводе информации стробирующий сигнал записи (  ), равный 0, свидетельствует о том, что ЦП произвел запись данных в выходной регистр канала. Входной сигнал подтверждения записи (

), равный 0, свидетельствует о том, что ЦП произвел запись данных в выходной регистр канала. Входной сигнал подтверждения записи (  ), равный 0, свидетельствует о том, что ВУ приняло данные. Сигнал INTR=1 информирует ЦП о завершении операции вывода информации из канала в ВУ. Сигнал INTR сбрасывается спадом сигнала

), равный 0, свидетельствует о том, что ВУ приняло данные. Сигнал INTR=1 информирует ЦП о завершении операции вывода информации из канала в ВУ. Сигнал INTR сбрасывается спадом сигнала  .

.

При вводе или выводе в режимах 1 или 2 важным является определение ЦП момента, когда можно читать или выдавать данные. При вводе ЦП должен определить наличие данных, переданных ВУ, в регистре канала для того, чтобы их прочитать. При выводе ЦП должен определить произошла ли передача данных из канала в ВУ, т.е. освободился ли канал для следующей передачи, что позволит ЦП послать в канал очередные данные.

Для определения момента чтения или посылки данных в канал ППИ ЦП должен определить состояние канала. Определение состояния каналов А и В можно реализовать двумя путями. Первый – схемная реализация. Для этого используется сигнал ППИ INTR (запрос прерывания), вызывающий прерывание работы ЦП для выполнения программы ввода или вывода данных в ППИ. Практически используется другой вариант – программная реализация чтения состояния каналов А или В, которое формируется в соответствующих разрядах регистра канала С (бит С3 для канала А, бит С0 для канала В).

Выработку ППИ сигнала прерывания разрешает бит INTE регистра канала С: второй разряд этого регистра – для канала В, четвертый и шестой разряды – для канала А в режимах ввода и вывода соответственно. Путем установки или сброса указанных разрядов программист может разрешить или запретить обслуживание любого ВУ при работе по прерываниям.

Установка или сброс разряда регистра канала С, в том числе и бита INTE, осуществляется ЦП засылкой слова по адресу РУС, т.е. при состоянии сигналов А1, А0=1,1. При этом разряд D7 РУС должен быть равен 0 (рис.1.6).

Рис. 1.6. Формат слова установки разряда регистра канала С

При посылке управляющего слова с D7=0 разряд регистра канала C, указанный в битах D3-D1, сбрасывается в 0, если D0=0, или устанавливается в 1, если D0=1.

Установка в 1 бита INTE разрешает выработку сигнала прерывания INTR. Разряды D6-D4 не используются.

Рассмотрим пример ассемблерных команд при работе с ППИ. Пусть в МПС для портов ППИ выделены адреса в диапазоне (80-83)Н. Линии адресной шины подключены к выводам А1, А0 ППИ соответственно. Для инициализации ППИ с параметрами: канал А (режим 1, вывод), канал В (режим 0, ввод), канал С (ввод) и установки бита INTE в 1 для канала А нужно выполнить следующие команды:

mov AL, 10101011B; инициализация ППИ

mov AL, 00001101B; установка бита 6

Для анализа состояния канала А с целью передачи очередного байта данных ЦП должен прочитать байт по адресу 82Н и определить состояние канала А по биту С3.

Контрольные вопросы и задания.

1. Сколько каналов ввода-вывода содержит ППИ? В каких режимах могут работать каналы ППИ?

2. Укажите назначение портов ввода-вывода ППИ.

3. В чем суть инициализации ППИ? Представьте формат управляющего слова ППИ.

4. Укажите на особенности во вводе-выводе через канал А в режиме 0 и в режиме 1.

5. Дайте назначение сигналов управления передачей данных через канал В режиме 1 при вводе и выводе данных.

6. В чем заключаются особенности работы канала А в режиме 2?

7. Для чего ЦП должен определять состояния каналов и как эта функция реализуется практически?

8. Для ППИ выделен диапазон адресов (84 – 87)H. Что означает выполнение следующих команд:

mov AL, 00001001B

Какую информацию несет передаваемый в ППИ байт?

9. Дано 12 тумблеров и 12 лампочек, предназначенных для индикации состояния тумблеров. Можно ли организовать с помощью ППИ ввод данных в МП о состоянии тумблеров с последующим выводов битов состояния на индикацию. Каким образом?

10. Дано 8 тумблеров и 8 лампочек индикации. Напишите ассемблерные команды для чтения состояния тумблеров через канал В ППИ (режим 0) и вывода байта состояния тумблеров на индикацию через канал А ППИ (режим 0). Перед командами ввода-вывода произвести инициализацию БИС в соответствии с заданием. Адреса портов БИС ППИ – (64-67) H.

1.2. Последовательный периферийный интерфейс

Для построения контроллеров, связывающих МПС на базе микропроцессора К1810 с ВУ, принимающими или передающими информацию в последовательном коде используется БИС КР580ВВ51А, представляющая собой универсальный синхронно-асинхронный приемопередатчик (УСАПП).

УСАПП преобразует поступающую с шины данных информацию из параллельного формата в последовательный для передачи в ВУ и преобразует принимаемую из ВУ в последовательном формате информацию в параллельный формат для выдачи её на шину данных МПС. Обмен информацией между УСАПП и ВУ может производиться в асинхронном или синхронном режимах.

В асинхронном режиме коды передаваемой информации разделяются специальными двоичными наборами. Каждое передаваемое слово передатчик сопровождает стартовым и стоповым битами, которыми осуществляется синхронизация запуска работы приемника. Формат передаваемого слова показан на рис. 1.7,а.

До начала передачи слова линия передачи данных находится в состоянии 1. Переход из 1 в состояние 0 отмечает начало передачи слова. Первый бит всегда содержит 0 и называется стартовым битом. Затем следуют 5¸8 информационных бит, первым из которых является младший бит слова, и необязательный бит четного или нечетного паритета.

Бит паритета используется для контроля ошибок, вызванных помехами на линии связи. При контроле по четности бит паритета устанавливается так, чтобы общее количество единиц в информационных битах и бите паритета было четным. В случае нечетного паритета количество единиц должно быт нечетным. Ошибка нечетной кратности в информационных битах и бите паритета изменяет четность единиц, что обнаруживается схемой контроля УСАПП.

Далее идут стоповые биты. Стоповые биты задают минимальное время, которое должно пройти перед стартовым битом следующего передаваемого слова, определяющее промежуток времени для обработки приемником принятой информации.

Рис 1.7. Формат передаваемой информации:

а) в асинхронном режиме; б) в синхронном режиме.

Передаваемая УСАПП в ВУ информация может иметь разные параметры, которые задаются путем программирования БИС. Отметим эти параметры и их значения при передаче в асинхронном режиме:

а) количество информационных бит в слове (5; 6; 7; 8);

б) тип паритета (четный; нечетный);

в) количество стоповых бит (1; 1,5; 2).

Кроме того, можно задавать скорость передачи информации. В БИС УСАПП при передаче данных в ВУ и при приеме данных из ВУ предназначены выводы для подключения внешнего генератора синхронизации для задания интервала каждого бита. Обычно при работе в асинхронном режиме частота внешних генераторов равна или в 16, или в 64 раза больше скорости передачи или приема (в бит/сек). Если, например, при приеме множитель равен 16, то после обнаружения перехода из 1 в 0 в начале символа узел приемника данных БИС должен отсчитать 8 импульсов синхронизации и опросить вход. При обнаружении 0 считается, что переход вызван стартовым битом, а не помехой. Тогда приемник данных БИС опрашивает вход через интервалы в 16 периодов импульсов синхронизации до ввода всех бит слова, включая и стоповые биты, после чего прекращает опрос и ожидает следующего перехода из 1 в 0 на входе. Величина значения множителя скорости передачи для асинхронного режима задается при программировании БИС.

В синхронном режиме данные передаются не по одному слову, а целыми массивами слов. Передаваемое слово также состоит из 5-8 информационных бит с необязательным битом паритета, но не имеет стартового и стопового битов. Число передаваемых информационных бит задается при программировании БИС и одинаково для всех слов. Передача любого массива слов всегда начинается с серии слов синхронизации, которые нельзя спутать с другими словами. Приемник констатирует факт начала сеанса передачи по совпадению этой серии с эталоном. Количество слов синхронизации может быть одно или два в зависимости от характера помех в линии передачи. Формат передаваемой информации в синхронном режиме представлен на рис. 1.7,б. Количество синхрослов задается при программировании БИС. Для обоих режимов если задается реализация контроля, то после каждого передаваемого слова добавляется бит паритета.

Структурная схема БИС УСАПП (КР580ВВ51А) приведена на рис. 1.8. Буфер данных является трехстабильным двунаправленным устройством для обмена данными и управляющими словами между ЦП и УСАПП. В его состав входят три 8-миразрядных регистра: регистр входных данных (Рвх  ), регистр выходных данных (Рвых), регистр состояния УСАПП (РС).

), регистр выходных данных (Рвых), регистр состояния УСАПП (РС).

Рис. 1.8. Структурная схема БИС УСАПП

При обмене данными с ВУ возникает необходимость контролировать состояние УСАПП. Для этой цели используется РС, в разрядах которого отображаются сбои, ошибки, возникающие при передаче и значения некоторых управляющих сигналов. ЦП может считывать содержимое РС УСАПП в любой момент времени.

Блок управления обеспечивает прием и хранение управляющих слов двух типов: инструкции режима в регистре режима (РР) и команды в регистре команд (РК). Инструкция вводится сразу после установки УСАПП в исходное состояние и заменяется лишь при смене режима. Команда осуществляет управление установленным режимом обмена и может многократно задаваться в процессе обмена, управляя различными его этапами.

Блок передачи обеспечивает преобразование параллельного 8-миразрядного кода, поступившего в УСАПП из ЦП в последовательный код. Основным узлом блока передачи является регистр передатчика (РПд), на входы которого поступают данные из РВх. Выдача информации в последовательном коде на выход передатчика (TxD) осуществляется путем сдвига данных в РПд.

Блок приема предназначен для преобразования данных, поступающих в последовательном коде на вход УСАПП (RxD) из ВУ, в параллельный восьмиразрядный код и передачи этого параллельного кода в Рвых буфера данных.

Блок регистров слов синхронизации состоит из двух регистров синхрослов (РСС). В эти регистры при работе УСАПП в синхронном режиме передачи ЦП записывает коды первого и второго слов синхронизации.

Блок управления принимает управляющие сигналы от ЦП и генерирует внутренние сигналы управления. На входы блока поступают: сигнал сброса (RESET), импульсы внутренней синхронизации УСАПП (CLK), сигналы чтения (  ), записи (

), записи (  ), выбора микросхемы (

), выбора микросхемы (  ) и сигнал «управление/данные» (C/

) и сигнал «управление/данные» (C/  ). При C/

). При C/  =0 выполняется запись данных с выводов D7-D0 в Рвх или чтение данных из Рвых на выводы D7-D0. При C/

=0 выполняется запись данных с выводов D7-D0 в Рвх или чтение данных из Рвых на выводы D7-D0. При C/  =1 – чтение из PС на D7-D0 или запись управляющих слов либо слов синхронизации одного или двух с D7-D0 в соответствующие регистры.

=1 – чтение из PС на D7-D0 или запись управляющих слов либо слов синхронизации одного или двух с D7-D0 в соответствующие регистры.

УСАПП занимает в адресном пространстве ввода-вывода МПС два адреса: А (четный адрес) и А+1 (нечетный адрес). При этом младший разряд адреса А0 подается на вход C/  . В табл.1.2 показаны сигналы управления, определяющие направление передачи и тип выполняемой операции. Как видно из табл.1.2 регистр режима, регистр команды, регистры слов синхронизации имеют один адрес. Выбор этих регистров зависит от последовательности обращения, схема которой представлена на рис. 1.9. После аппаратного сброса по сигналу RESET или по команде с установленным в 1 битом сброса следующий вывод по нечетному адресу (с А0=1,

. В табл.1.2 показаны сигналы управления, определяющие направление передачи и тип выполняемой операции. Как видно из табл.1.2 регистр режима, регистр команды, регистры слов синхронизации имеют один адрес. Выбор этих регистров зависит от последовательности обращения, схема которой представлена на рис. 1.9. После аппаратного сброса по сигналу RESET или по команде с установленным в 1 битом сброса следующий вывод по нечетному адресу (с А0=1,  =1 и

=1 и  =0) выполняется в регистр режима. Форматы регистра режима и регистра команд рассмотрены ниже. Если режим синхронный, то следующие один или два выводимых байта по нечетному адресу (А0=1) загружаются в регистры слов синхронизации. Количество синхрослов определяется информацией в регистре режима. Все последующие байты в синхронном и асинхронном режимах направляются в регистр команды (если А0=1) или в передатчик (если А0=0). Таким образом, для правильной работы УСАПП инструкция режима и управляющая команда должны следовать в строго определенном порядке.

=0) выполняется в регистр режима. Форматы регистра режима и регистра команд рассмотрены ниже. Если режим синхронный, то следующие один или два выводимых байта по нечетному адресу (А0=1) загружаются в регистры слов синхронизации. Количество синхрослов определяется информацией в регистре режима. Все последующие байты в синхронном и асинхронном режимах направляются в регистр команды (если А0=1) или в передатчик (если А0=0). Таким образом, для правильной работы УСАПП инструкция режима и управляющая команда должны следовать в строго определенном порядке.

Рис. 1.9. Схема алгоритма вывода байт управления

Важной функцией блока управления является квитирование обменов с ВУ (терминалом). На выходах блока управления формируются сигналы запроса передатчика терминала на передачу данных (  ) и запроса приемника на прием данных (

) и запроса приемника на прием данных (  ). На выходы блока управления поступают сигналы готовности терминала передать данные (

). На выходы блока управления поступают сигналы готовности терминала передать данные (  ) и принять данные (

) и принять данные (  ). При этом квитируется только начало обмена.

). При этом квитируется только начало обмена.

Блок передачи предназначен для приема данных из РВх и выдачи их в последовательном коде на выход (TxD), а также для приема сигнала синхронизации передатчика (TxC) и формирования сигналов окончания передачи (TxE) и готовности передатчика (TxRDY).

Блок приема принимает данные в последовательном коде от ВУ (RxD) и преобразует их в параллельный формат. Кроме этого, блок приема принимает сигналы синхронизации приемника (RxC); формирует сигнал готовности приемника (RxRDY); имеет программируемый двунаправленный вывод SYNDET. В режиме синхронного ввода с внутренней синхронизацией SYNDET служит выходом, на котором формируется 1 при обнаружении слова (слов) синхронизации во входном двоичном потоке. Если же поиск слов синхронизации осуществляется внешним связным оборудованием, то на вход SYNDET подается единичный сигнал о фиксации соответствия. В асинхронном режиме SYNDET является выходом, сигнал 1 на котором называется сигналом обнаружения разрыва. Этот сигнал отмечает прием слова, состоявшего из одних нулей.

Форматы управляющих слов

При программировании УСАПП необходимо закодировать и записать в БИС инструкцию режима и команду управления. Форматы инструкций режима для асинхронного и синхронного режимов работы показаны на рис. 1.10, а формат команды управления на рис. 1.11.

Рис. 1.10. Формат инструкции режима:

а) для асинхронного режима; б) для синхронного режима.

Рис. 1.11. Формат команды управления

Инструкция режима определяет количество информационных бит, наличие или отсутствие контроля паритета, вид контроля для символа, передаваемого синхронно или асинхронно. При синхронном режиме два младших бита инструкции равны 0, два старших определяют количество символов синхронизации и режим использования вывода SYNDET – как входа или выхода. В асинхронном режиме два старших разряда определяют количество стоповых бит, два младших разряда – множитель скорости передачи или приема. В синхронном режиме скорости (в бит/сек) передачи или приема, т.е. сдвига в регистрах передатчика или приемника, совпадают с частотами синхронизации по входам ТхС и RхС соответственно. В асинхронном режиме частоты синхронизации на входах ТхС и RхС равны скорости передачи или приема, умноженной на 1, 16 или 64.

БИС УСАПП содержит регистр состояния РС, позволяющий ЦП читать состояние БИС в любой момент времени в процессе выполнения операции. Формат слова состояния БИС показан на рис. 1.12.

Рис. 1.12. Формат слова состояния

В РС биты D6, D2 и D1 отражают состояния соответствующих выводов УСАПП. В отличии от сигнала на выводе TxRDY, на состояние бита D0 (равного 1, если РВых свободен) не влияет входной сигнал  или бит D0 регистра команд. Биты RxRDY и TxRDY можно использовать для программного ввода-вывода, а сигналы с соответствующих выводов УСАПП можно подключить к линиям запросов прерываний для организации ввода-вывода по прерываниям. Бит TxRDY автоматически сбрасывается, когда имеется символ для передачи, а бит RxRDY – когда установивший его символ введен в ЦП. Бит D2 (TxE) показывает, что регистр сдвига передатчика ожидает загрузки символа из РВых.

или бит D0 регистра команд. Биты RxRDY и TxRDY можно использовать для программного ввода-вывода, а сигналы с соответствующих выводов УСАПП можно подключить к линиям запросов прерываний для организации ввода-вывода по прерываниям. Бит TxRDY автоматически сбрасывается, когда имеется символ для передачи, а бит RxRDY – когда установивший его символ введен в ЦП. Бит D2 (TxE) показывает, что регистр сдвига передатчика ожидает загрузки символа из РВых.

После загрузки инструкции режима, символов синхронизации и команды УСАПП готов к выполнению обмена данными в одном из 5 режимов: асинхронная передача, асинхронный прием, синхронная передача, синхронный прием с внутренней синхронизацией, синхронный прием с внешней синхронизацией.

При асинхронной передаче в УСАПП загружается команда с D0=1 («разрешение передачи») и D5=1, что означает формирование устройством запроса  =0 (рис. 1.11). Затем командой вывода OUT ЦП выдает в УСАПП из аккумулятора первый байт данных. Если далее на вход

=0 (рис. 1.11). Затем командой вывода OUT ЦП выдает в УСАПП из аккумулятора первый байт данных. Если далее на вход  поступит сигнал 0, свидетельствующий о готовности приемника терминала принять данные, то принятый в УСАПП байт данных вместе со стартовым битом, битом паритета и стоповыми битами будет выдаваться на выход TxD по спаду сигнала синхронизации TxC с периодом, задаваемым инструкцией режима и равным 1, 16 или 64 периодам сигнала TxC.

поступит сигнал 0, свидетельствующий о готовности приемника терминала принять данные, то принятый в УСАПП байт данных вместе со стартовым битом, битом паритета и стоповыми битами будет выдаваться на выход TxD по спаду сигнала синхронизации TxC с периодом, задаваемым инструкцией режима и равным 1, 16 или 64 периодам сигнала TxC.

Завершение выдачи символа УСАПП сигнализирует установкой бита готовности передатчика в РС (бит D0). Следовательно, окончание процесса выдачи УСАПП байта можно установить, цик

УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801[1]

Изготовление БИС на основе БМК заключается в формировании с помощью двух

верхних слоёв (слой металлизации и слой контактов) разветвлённых связей необходимой

конфигурации между ячейками БМК. Процесс проектирования и изготовления БИС осуществляется

в несколько этапов (техническое задание, ввод исходной информации, логическое

моделирование, синтез тестов, трассировка связей, расчёт паразитных элементов

связей, расчёт электрической схемы) с помощью автоматизированной системы проектирования.

На основе БМК К1801ВП1 спроектировано несколько сотен различных заказных схем

в основном частного применения, т. е. предназначенных для конкретной аппаратуры.

В разделе «Справочная информация» будут рассмотрены универсальные интерфейсные

БИС, получившие наиболее широкое распространение:

- К1801ВП1-030 – устройство управления блоками ОЗУ динамического типа;

- К1801ВП1-033 – многофункциональное устройство, позволяющее реализовать

интерфейс накопителя на гибких магнитных дисках, контроллер интерфейса параллельного

ввода-вывода, контроллер байтового параллельного интерфейса; - К1801ВП1-034 – многофункциональное устройство, предназначенное для организации

устройства передачи данных, устройства выдачи вектора прерывания и компаратора

адреса, буферного регистра данных; - К1801ВП1-035 – контроллер внешних устройств, работающих на линию связи

с последовательной передачей данных.

Все микросхемы изготавливаются по n-канальной МОП-технологии в керамических

42-выводных корпусах типа 429.42-5. Основные параметры микросхем приведены в

табл. 1.

В этом номере журнала представлена микросхема К1801ВП1-030. Остальные интерфейсные

БИС комплекта К1801 и рекомендации по их применению будут рассмотрены в последующих

номерах.

Микросхема К1801ВП1-030

Предназначена для использования в блоках ОЗУ, выполненных на основе микросхем

К565РУЗ с динамическим хранением данных, в качестве устройства управления (контроллера)

обменом данных. Условное графическое обозначение микросхемы дано на рис. 1,

назначение выводов приведено в табл. 2. Номер ТУ: оКО.348.740-0301 ТУ.

Контроллер рассчитан на управление блоком ОЗУ ёмкостью 16К 16-разрядных слов,

выполненном на 16 микросхемах серии К565РУЗ, или двумя полублоками. Микросхема

осуществляет следующие функции:

- приём, хранение и преобразование адреса для накопителя ОЗУ;

- регенерацию памяти;

- обмен информацией по системной магистрали микро-ЭВМ «Электроника 60»;

- выработку вспомогательного сигнала блокирования LOCK при обращении в

область внешних устройств (старшие 4К слов). Сигнал LOCK предназначен для

использования БИС К1801ВП1-030 совместно с микропроцессором К1801ВМ1.

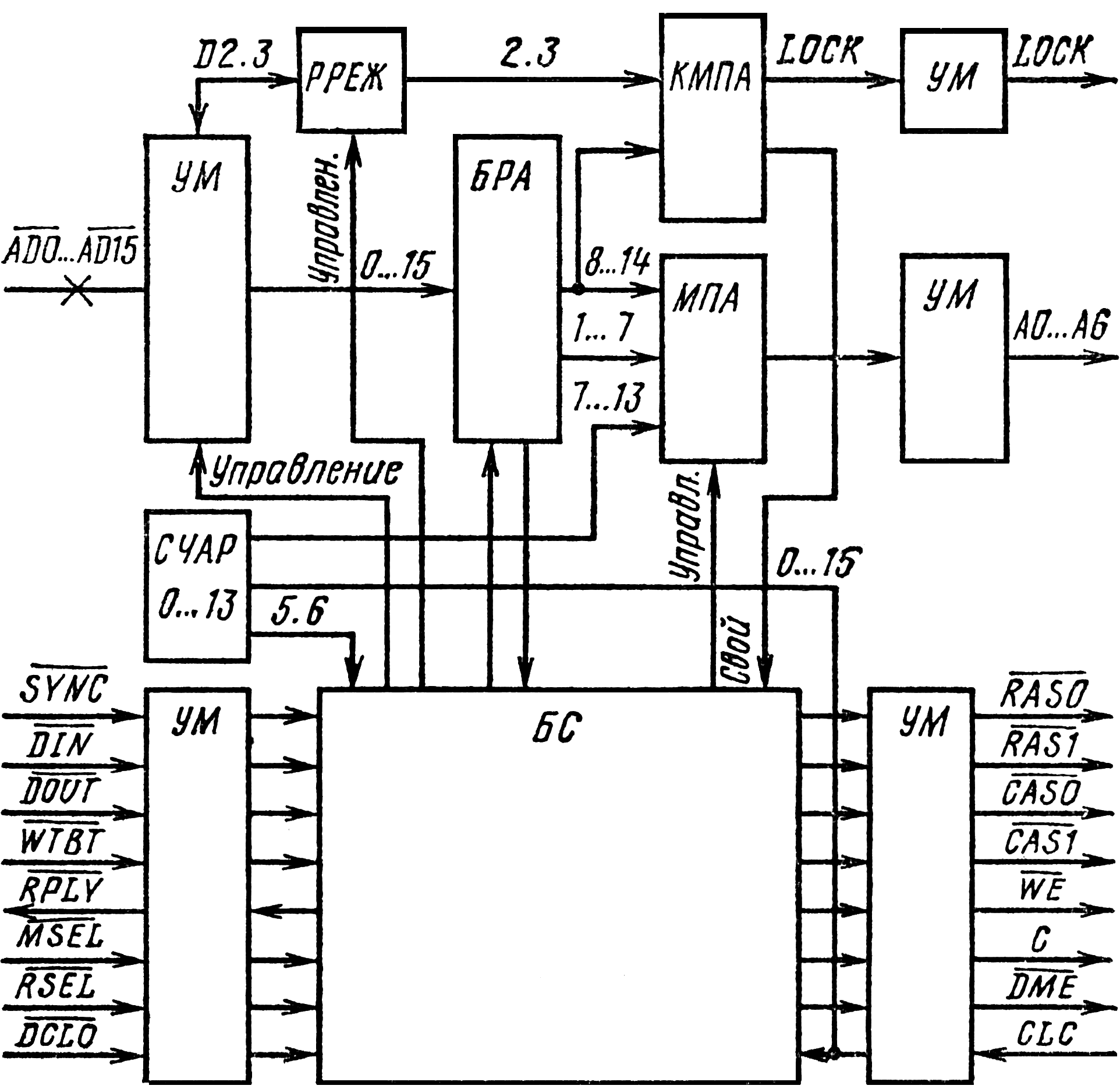

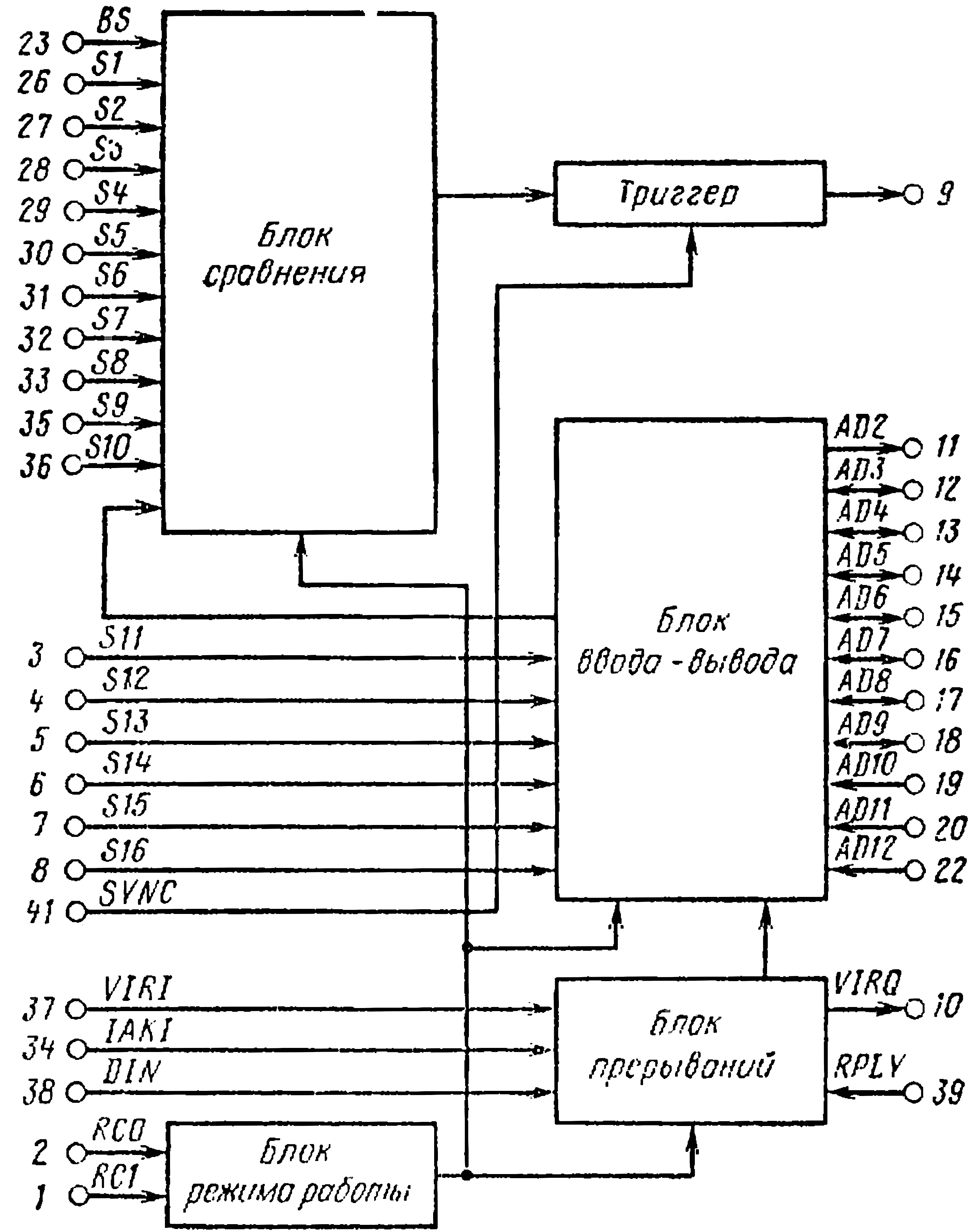

Структурная электрическая схема контроллера ОЗУ (рис. 2) включает счётчик

адресов регенерации (СЧАР), буферный регистр адреса (БРА), мультиплексор адресов

(МПА), регистр режима (РРЕЖ), компаратор адресов (КМПА), блок синхронизации

(БС), буферные усилители мощности (УМ).

Рис. 2. Электрическая структурная схема микросхемы К1801ВП1-030

Мультиплексор МПА служит для раздельной во времени выдачи адреса ОЗУ в виде

7-разрядных адресов строки и столбца в циклах обмена с накопителем ОЗУ, а также

7-разрядного адреса регенерации.

Вспомогательный регистр режима РРЕЖ предназначен для дублированного хранения

служебных признаков режимов работы «останов» и «расширенная арифметика» микропроцессора

К1801ВМ1. Содержит два разряда РРЕЖ2 и РРЕЖЗ, доступных по чтению и записи из

канала (разряды AD2 и AD3 соответственно). Режиму «останов» соответствует значение

единицы в разряде РРЕЖ2, режиму «расширенная арифметика» – в разряде РРЕЖЗ.

Информация, хранимая в РРЕЖ, влияет на установку сигнала LOCK.

Компаратор адресов КМПА вырабатывает сигнал блокировки LOCK, который служит

для выборки областей адресов из системного ПЗУ и блокировки этих областей в

адресном пространстве внешних устройств.

Сигнал LOCK устанавливается в следующих случаях:

- адрес обращения находится в диапазоне 1600008 … 1637778

(режим «останов»); - адрес обращения – в диапазоне 1600008 … 1737778

(режим «расширенная арифметика»); - адрес обращения – в диапазоне 1730008 … 1737778

(независимо от состояния режимов РРЕЖ2 и РРЕЖЗ).

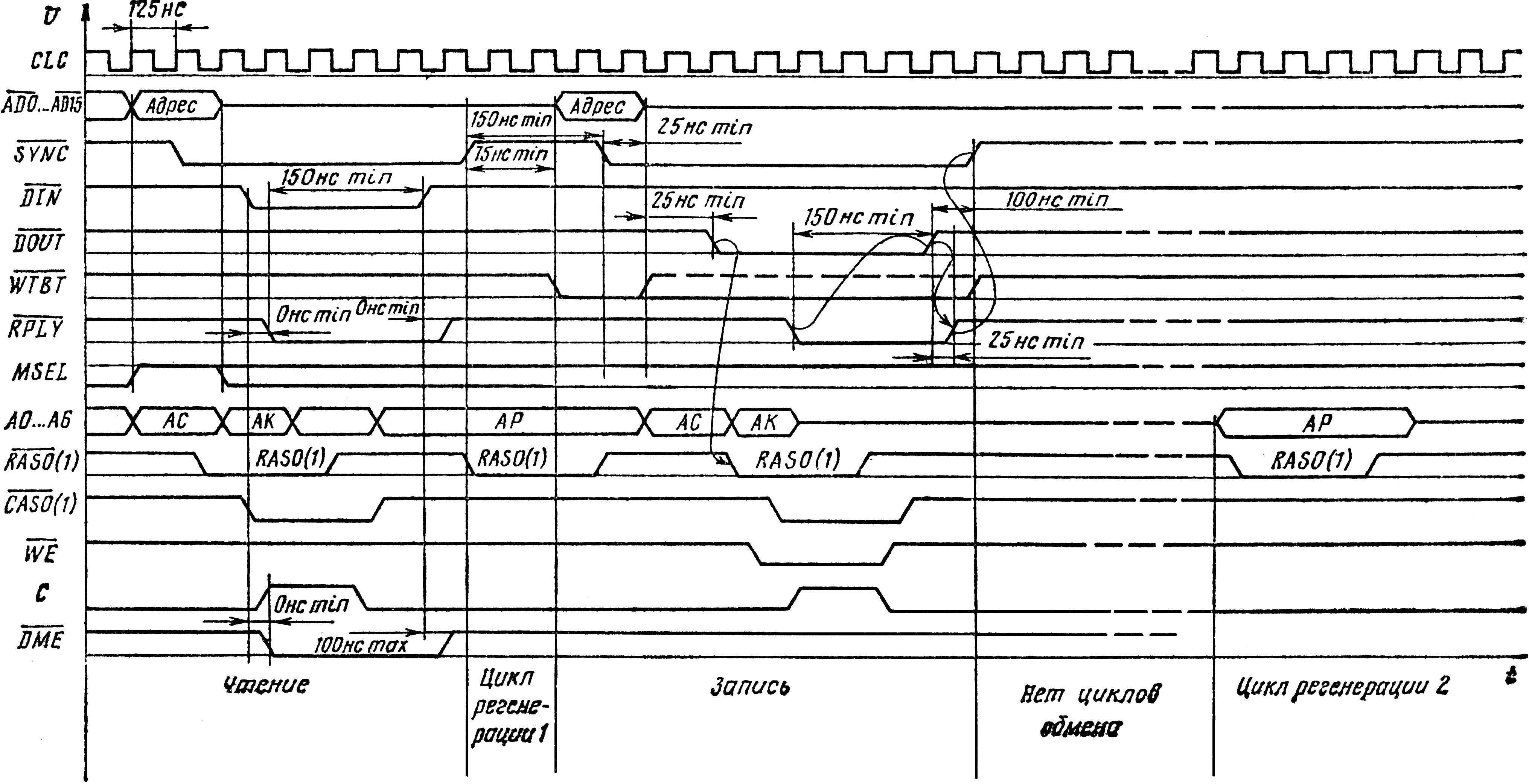

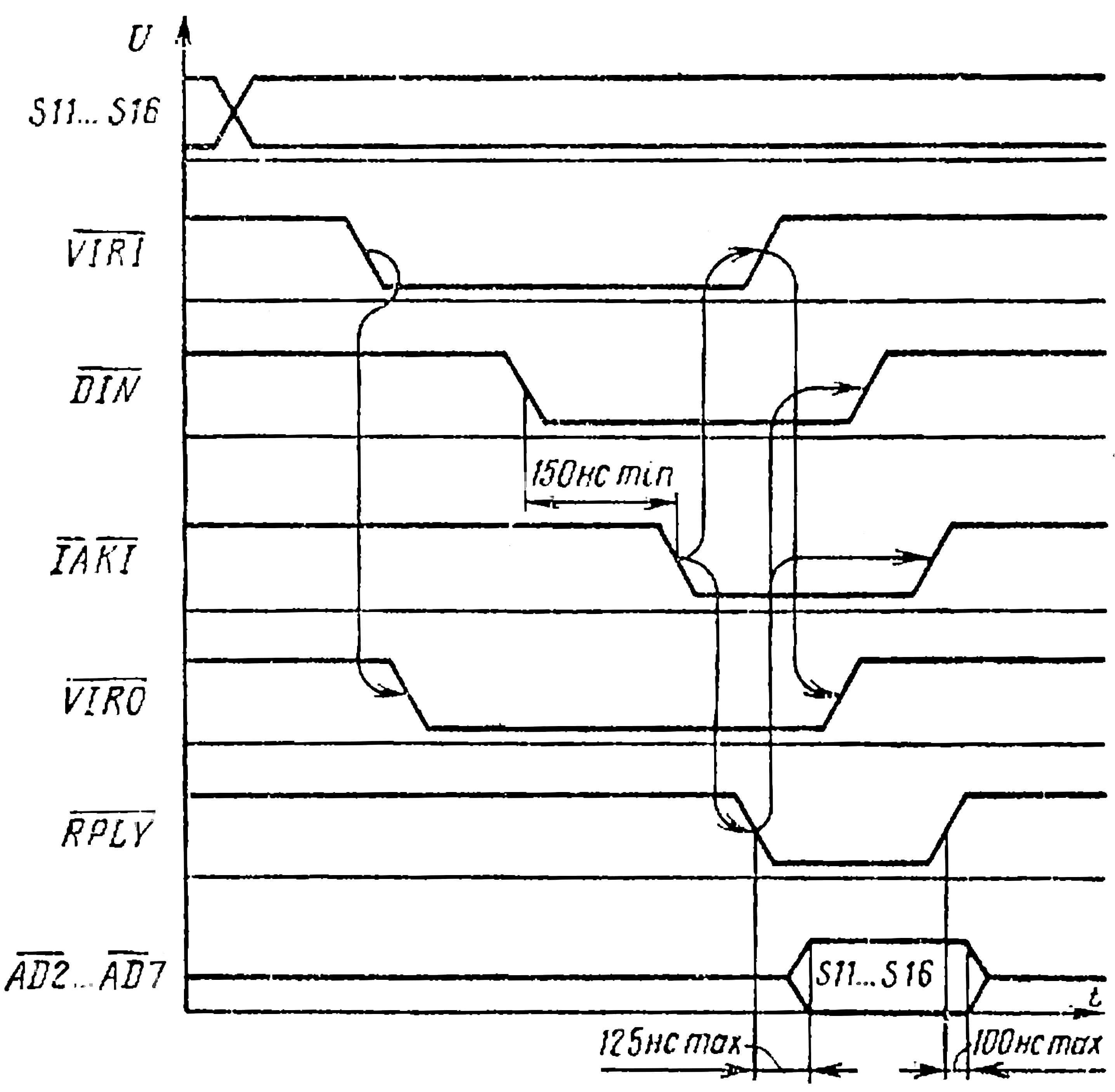

Рис. 3. Временная диаграмма работы микросхемы управления ОЗУ

К1801ВП1-030

Блок синхронизации БС вырабатывает сигналы управления внутренними узлами

микросхемы, накопителем ОЗУ, внешним буферным регистром данных, а также отрабатывает

сигнал управления по системной магистрали ЭВМ.

Режим работы контроллера

Регенерация (восстановление) информации в памяти динамического типа происходит

по принципу: один цикл регенерации – по одному адресу строки в течение 15,6 мкс.

Полная регенерация по всем адресам наступает через 2 мс. В БС введена схема

подсинхронизации запуска текущего цикла регенерации к окончанию цикла обмена

информацией (цикл регенерации 1), что делает память динамического типа максимально

прозрачной для процессора (рис. 3). При отсутствии циклов обмена с памятью

в течение 8 мкс после получения БС запроса на регенерацию очередной цикл

регенерации наступает принудительно, без подсинхронизации (цикл регенерации

2).

Сигналы и

вырабатываются одновременно.

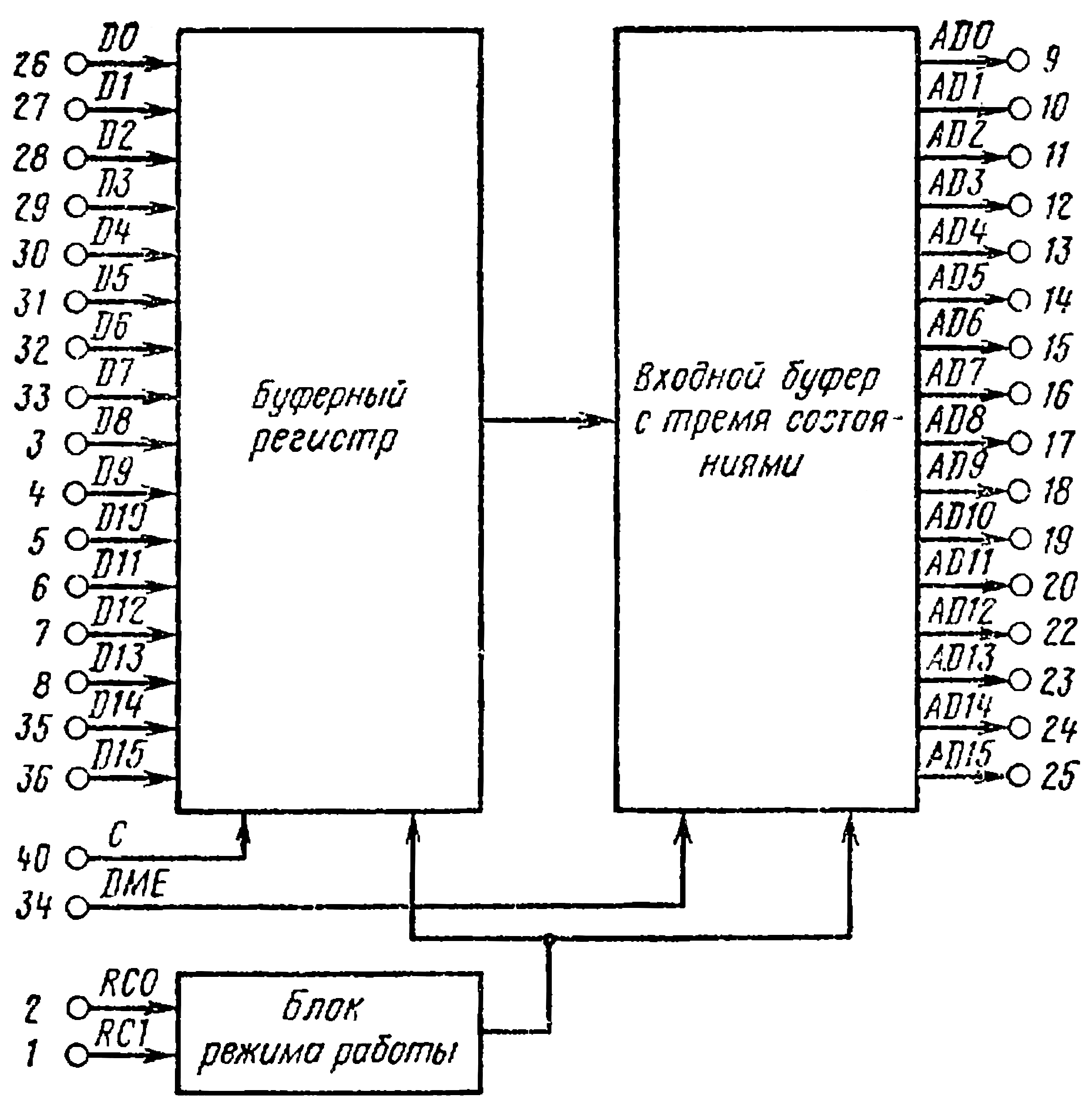

Временная диаграмма работы БИС К1801ВП1-030 в режиме чтения показана на рис. 3.

Выходные сигналы и

микросхема вырабатывает только при наличии сигнала .

Сигнал устанавливается в фазе выдачи адреса,

если =1. При

=0 формируется сигнал

. Сигналы и

вырабатываются одновременно.

Запись в память вызывают следующие сигналы:

- , фиксирующий адрес обращения

… в БРА; - и , которые

фиксируются в элементах хранения БС; - сигнал , а также отсутствие очередного

цикла регенерации памяти.

Временная диаграмма работы контроллера в режиме записи так же приведена на

рис. 3.

Наличие сигнала в фазе выдачи адреса является

признаком записи слова, а в фазе выдачи данных – признаком записи байта. При

модификации «запись байта» БС вырабатывает сигнал ,

если =1 в фазе выдачи адреса. Если

=0, устанавливается сигнал . При модификации «запись слова» сигналы

и вырабатываются одновременно.

Начальная установка. Микросхема приходит в состояние готовности за время,

соответствующее длительности прохождения семи синхронизирующих импульсов CLC.

Сигнал устанавливает СЧАР в нулевое состояние

и РРЕЖ в режим «останов».

ЛИТЕРАТУРА

Тел. 208-73-23, Москва, Г. Г. Глушкова

УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801

(Продолжение цикла. Начало в

№ 4, 5,

1988)

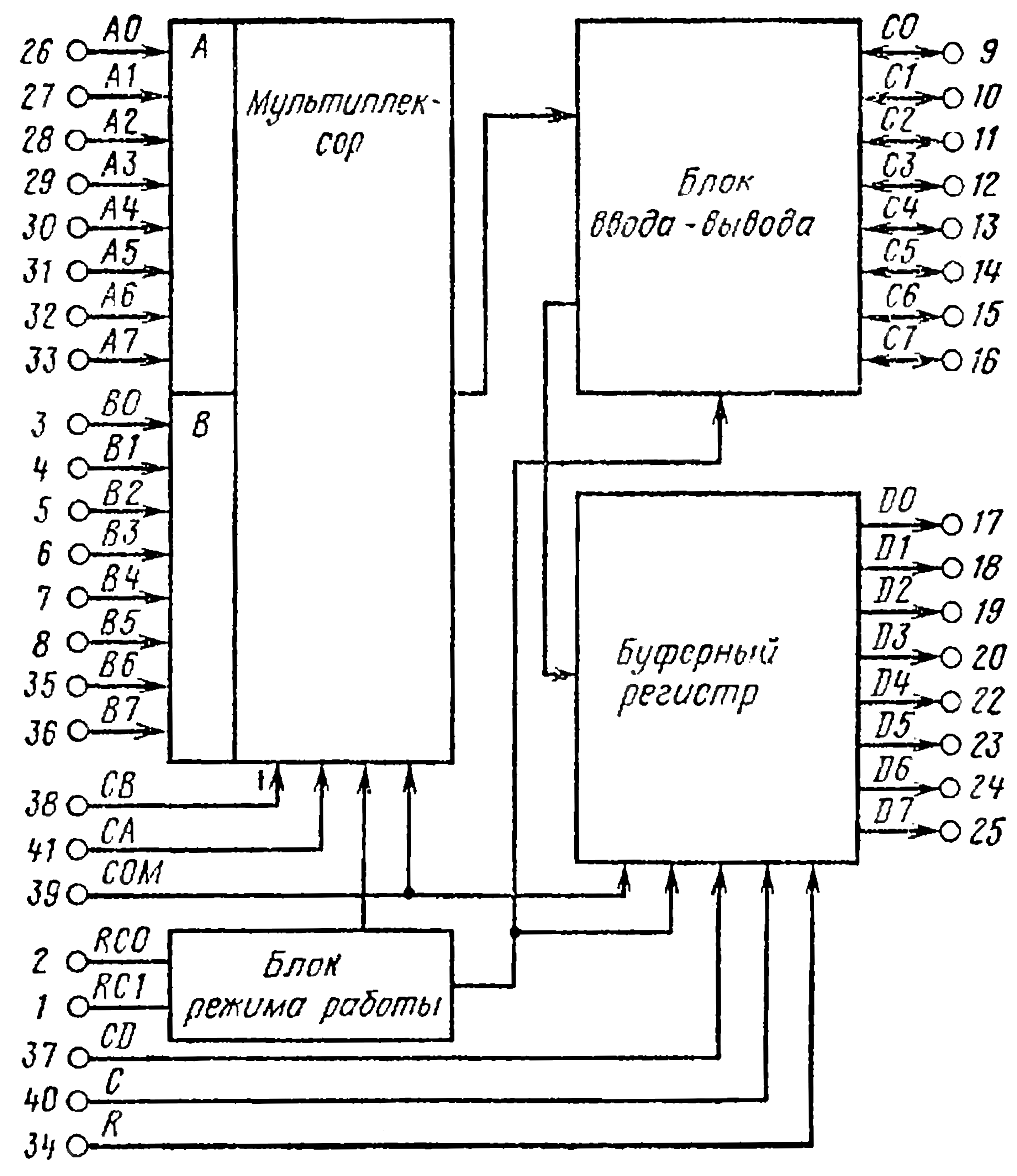

Микросхема К1801ВП1-034 представляет собой многофункциональное устройство,

работающее в следующих режимах:

- передачи информации;

- выдачи вектора прерывания и как компаратор адреса;

- буферного регистра данных.

Режим передачи информации

Условное графическое обозначение микросхемы К1801ВП1-034 в этом режиме приведено

на рис. 1, назначение выводов показано в табл. 1, электрическая структурная

схема представлена на рис. 2.

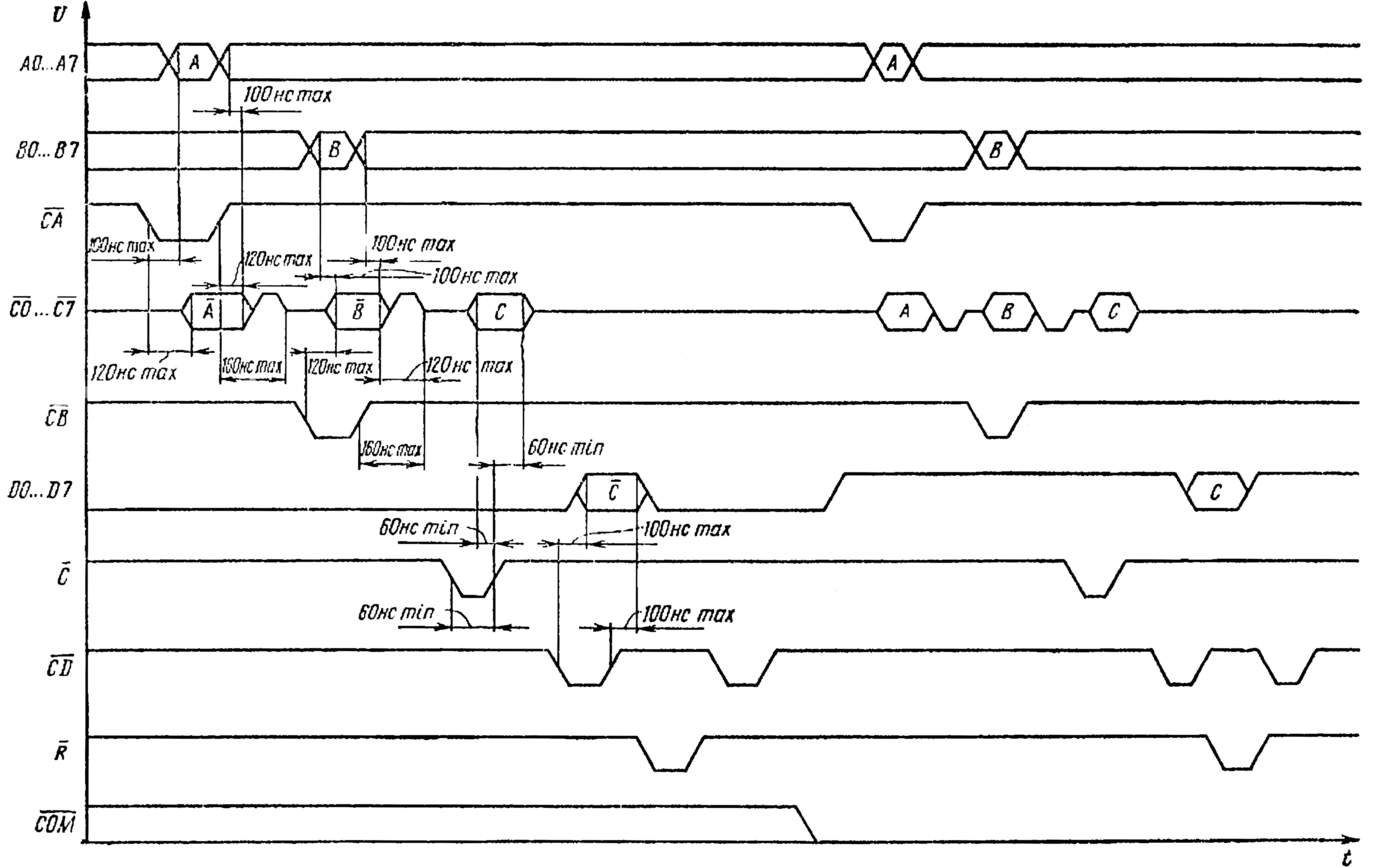

Рис. 2. Электрическая структурная схема устройства передачи

информации

Рис. 3. Временная диаграмма работы устройства передачи информации

Режим выдачи вектора прерывания и компаратора адреса.

Условное графическое обозначение микросхемы в этом режиме дано на рис. 4,

назначение выводов доказано в табл. 2, электрическая структурная схема

приведена на рис. 5.

Рис. 5. Электрическая структурная схема устройства выдачи

вектора прерывания и компаратора адреса

Рис. 6. Временная диаграмма работы устройства выдачи вектора

прерывания

Рис. 7. Временная диаграмма работы компаратора адреса

Режим буферного регистра

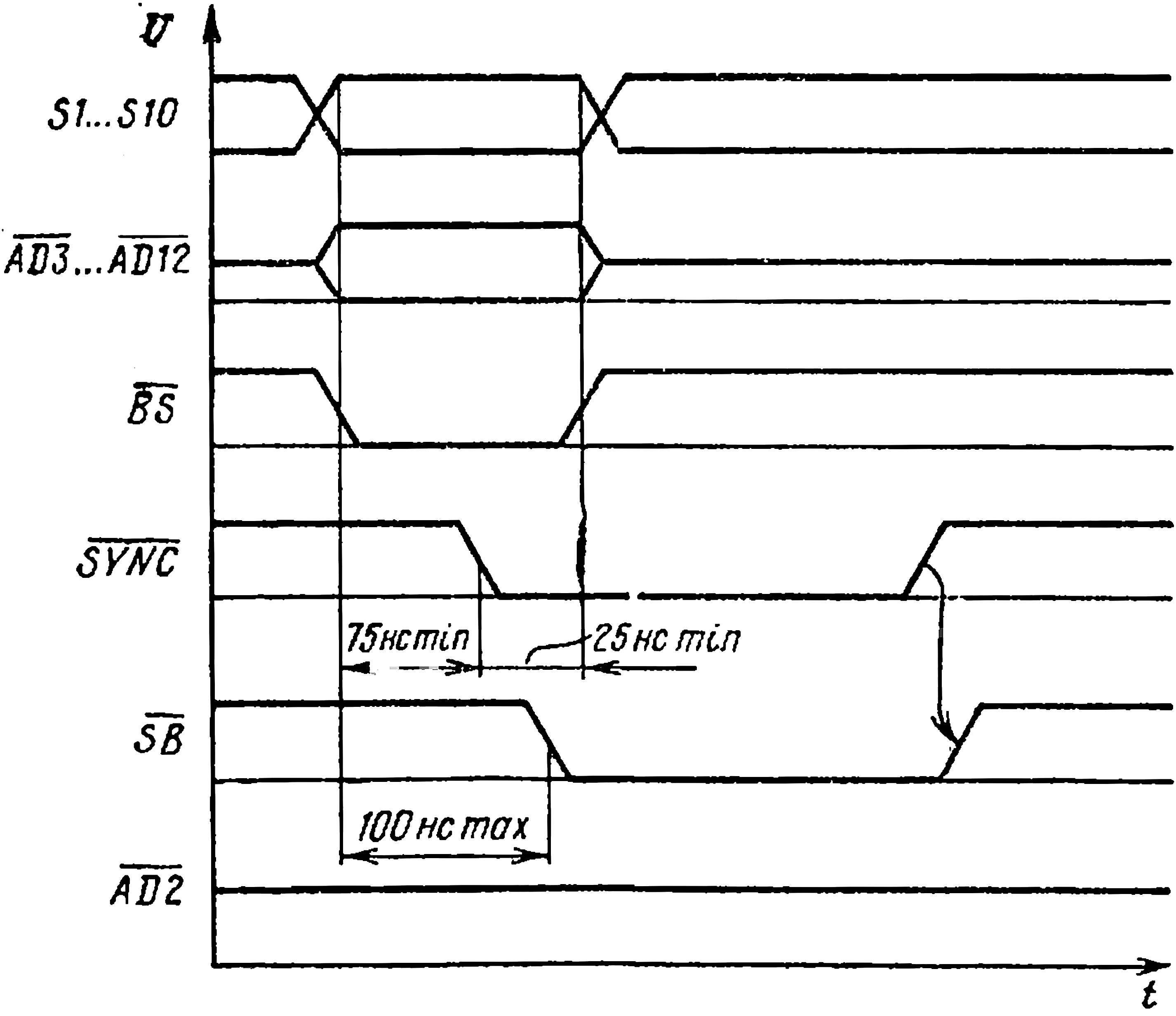

Этот режим устанавливается при напряжении низкого уровня на выводе RC0 и

высокого уровня на RC1. Условное графическое обозначение БИС К1801ВП1-034 в

указанном режиме приведено на рис. 8, назначение выводов показано в табл. 3,

электрическая структурная схема дана на рис. 9.

Рис. 9. Электрическая структурная схема буферного регистра

данных

Рис. 10. Временная диаграмма режима буферного регистра данных

Г.Г. Глушкова, телефон: 208-73-23, Москва